Conceptual diagram of two data flows used in the experiment: Output... | Download Scientific Diagram

An Energy-Efficient Deep Convolutional Neural Network Inference Processor With Enhanced Output Stationary Dataflow in 65-nm CMOS

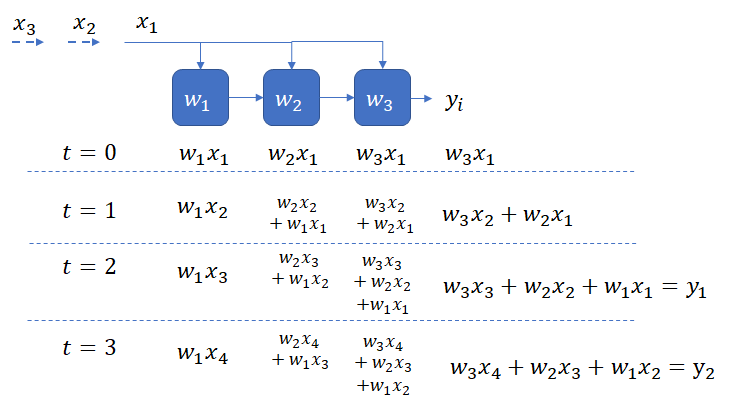

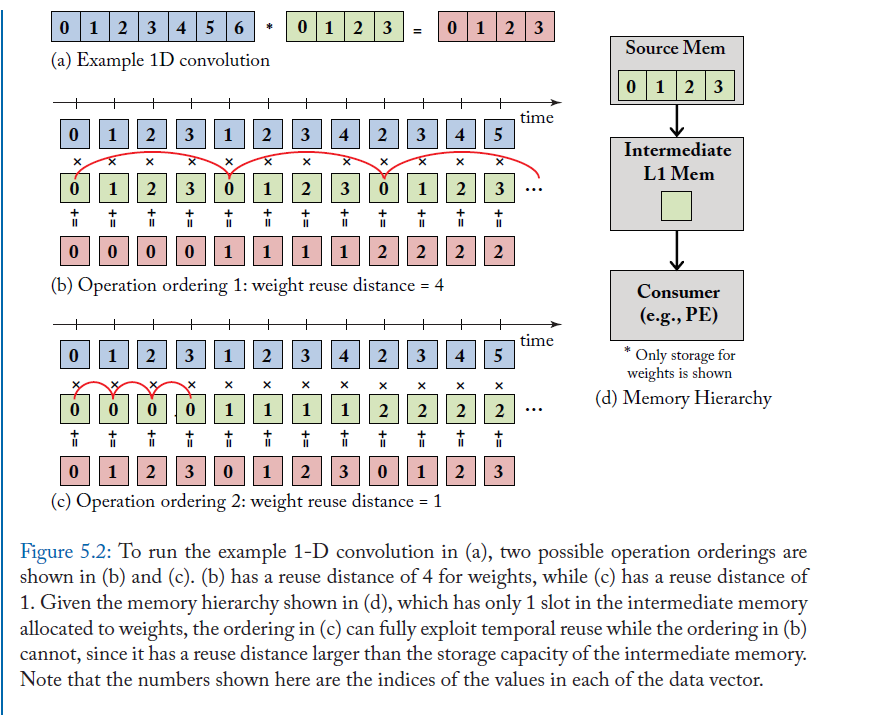

CS295: Modern Systems: Application Case Study Neural Network Accelerator – 2 Sang-Woo Jun Spring 2019 Many slides adapted from Hyoukjun Kwon's Gatech. - ppt download

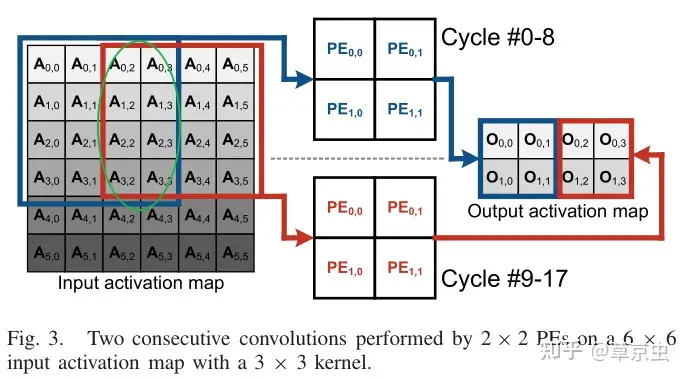

An Energy-Efficient Deep Convolutional Neural Network Inference Processor With Enhanced Output Stationary Dataflow in 65-nm CMOS

Reconfigurable Dataflow Optimization for Spatiotemporal Spiking Neural Computation on Systolic Array Accelerators

An Energy-Efficient Deep Convolutional Neural Network Inference Processor With Enhanced Output Stationary Dataflow in 65-nm CMOS | Semantic Scholar

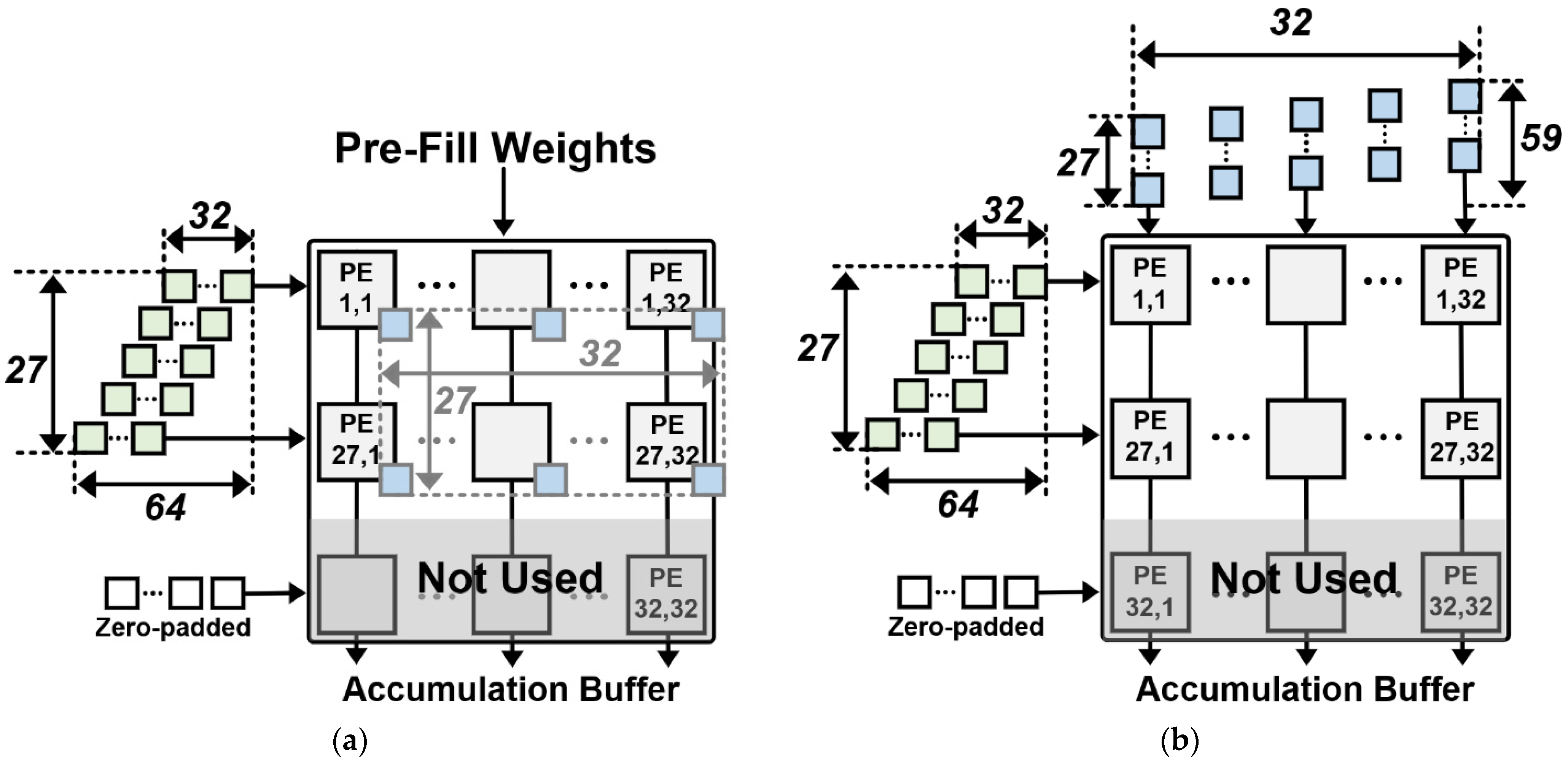

Electronics | Free Full-Text | CONNA: Configurable Matrix Multiplication Engine for Neural Network Acceleration

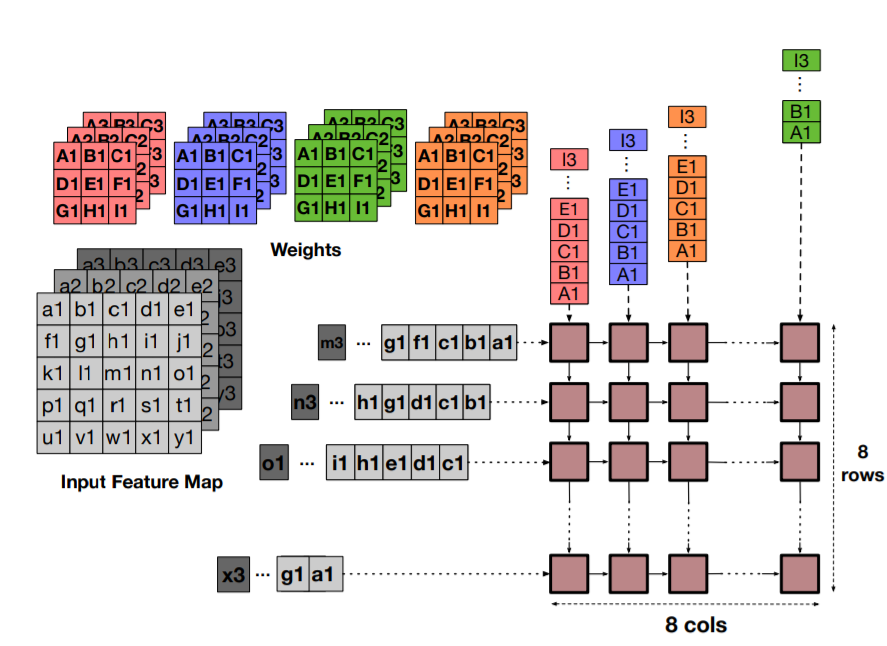

Illustrations of a weight stationary and b output stationary data flows | Download Scientific Diagram

![Sparse Tensor Accelerator Modeling Tutorial @ ISCA 2021 [Part 1] (3/7) - YouTube Sparse Tensor Accelerator Modeling Tutorial @ ISCA 2021 [Part 1] (3/7) - YouTube](https://i.ytimg.com/vi/q6xaSUYPo7g/hqdefault.jpg?sqp=-oaymwEmCOADEOgC8quKqQMa8AEB-AH-DoACuAiKAgwIABABGGIgYihiMA8=&rs=AOn4CLB94fclzf0sQbzOhw18k48kNEOxDQ)